Makefile编写

程序的编译和链接

使用C、C++编写可执行文件,首先要把源文件编译成中间代码文件,Linux下是.o文件,即Object File,这个动作叫做编译(complie)。

然后再把大量的Object File合成执行文件,这个动作叫链接(link)。

一个项目会拥有成百上千个源程序文件,再使用G++ or GCC会很麻烦。于是Makefile闪亮登场。

Makefile确定整个工程的编译规则,只需要一个make命令,就可以实现“自动化编译”。

make是一个解释Makefile中指令的命令工具,一般来说,大多数的IDE都有这个命令,比如:Delphi的make,Visual C++的nmake,Linux下的GNU的make。

Make工作原理

通常在一个项目中,我们的规则是:

- 如果这个工程没有被编译过,那么我们的所有C文件都要编译并被链接。

- 如果这个工程的某几个C文件被修改过,那么我们只需要编译被修改的那几个C文件,并链接成生可执行文件。(链接目标程序)

- 如果这个工程的头文件被改变了,那么我们需要编译引用了这个几个头文件的C文件,并链接生成可执行文件。(链接目标程序)

只要我们的Makefile写的够好,我们只用一个make命令就可以完成,make命令会自动智能地根据当前文件的修改情况来确定哪些文件需要重新编译,从而自己编译需要的文件和链接生成可执行文件。

Makefile的规则:

target ... :prerequisites...

command

...

...

- target是一个目标文件,可以是Object File,也可以是可执行文件。还可以是一标签。

- prerequisites就是要生成那个target所需要的文件或是目标。

- command就是make需要执行的命令。(任意的Shell命令)

这是一个文件依赖关系,也就是说,target这一个或多个的目标文件依赖于prerequisites中的文件,其生成规则定义要在command中。说白一点,prerequisites中如果有一个以上的文件比target文件要新的话,command所定义的命令就会被执行。

这就是Makefile的规则,也就是Makefile中最核心的内容。

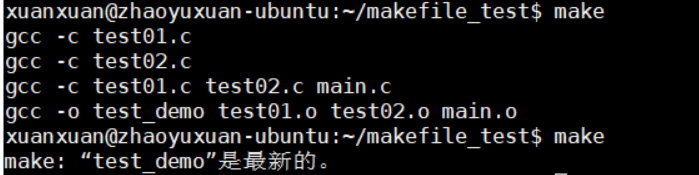

示例:

test_demo:test01.o test02.o main.o

gcc -o test_demo test01.o test02.o main.o

test01.o:test01.h test01.c

gcc -c test01.c

test02.o:test02.h test02.c

gcc -c test02.c

main.o: test01.h test01.c test02.h test02.c main.c

gcc -c test01.c test02.c main.c

clean:

rm test_demo test01.o test02.o main.oMake工作流程

- make会在当前目录下找到名字叫做"Makefile" 或 "makefile"的文件。

- 如果找到,它会找文件中的第一个目标文件(target),例如上面示例中的test_demo,并把这个文件作为最终的目标文件。

- 如果目标文件(target)不存在,或是target后依赖的.o文件的文件修改时间要比目标文件新,那么,它就会执行后面所定义的命令来重新生成目标文件。

- 如果目标文件(target)所依赖的.o文件也不存在,那么make会在当前文件中找目标为.o文件的依赖,如果找到则再根据那个规则生成.o文件。

- 如果文件依赖都齐全,则会正常执行,先生成.o文件,再链接生成目标文件。

Make变量

一个Makefile中我们发现经常会有重复的内容,例如上面示例中的:

test01.o test02.o main.o如果我们需要再加入一个新的.o文件,那么好几个地方都需要修改,可能会忘记并导致编译失败。

所以,为了makefile的易维护,在makefile中我们可以使用变量。makefile的变量也就是一个字符串。可以理解为C语言中的宏。

变量定义:

objects = test01.o test02.o main.o # 使用Shell script的语法示例:

objects = test01.o test02.o main.o

test_demo: $(objects)

gcc -o test_demo $(objects)

test01.o:test01.h test01.c

gcc -c test01.c

test02.o:test02.h test02.c

gcc -c test02.c

main.o: test01.h test01.c test02.h test02.c main.c

gcc -c test01.c test02.c main.c

clean:

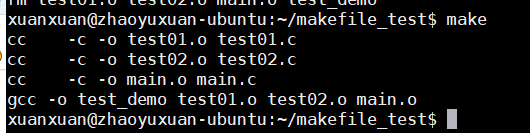

rm $(objects) test_demoMake自动推导

make很强大, 它可以自动推导文件以及文件依赖关系后面的命令,于是我们就没必要去在每一个.o文件后写上类似的命令,因为make会自动识别,自己推导命令。

只要make看到一个.o文件,它就会自动地把.c文件加在依赖关系中,如果make找到一个test01.o,那么test01.c就是它的依赖文件。并且gcc -c test01.c也会被推导出来。

示例:

objects = test01.o test02.o main.o

test_demo: $(objects)

gcc -o test_demo $(objects)

test01.o:test01.h

test02.o:test02.h

main.o: test01.h test02.h

clean:

rm $(objects) test_demo还可以再简洁些

objects = test01.o test02.o main.o

test_demo: $(objects)

gcc -o test_demo $(objects)

$(objects):test01.h test02.h

clean:

rm $(objects) test_demo

关于我:

评论区